Автореферат

Введение

Цель и задачи работы

Предполагаемая научная новизна

Планируемая практическая ценность

Обзор существующих разработок по теме

Текущие и планируемые результаты

Заключение и выводы

Список источников

Введение

Важнейшей частью любого цифрового устройства является управляющий автомат. Устройство управления может быть реализовано в виде автомата с программируемой логикой или автомата с жесткой логикой. В последнее время все чаще для реализации управляющих автоматов с жесткой логикой применяются программируемые логические интегральные схемы (ПЛИС).

Это связано с тем, что за последние тридцать лет произошел взрывной рост плотности интеграции схем, что привело к возможности выпуска схем содержащих на одном кристалле миллионы логических вентилей. В результате стало возможным реализация сложных цифровых устройств на нескольких, или даже одной БИС.

В настоящее время выпускаемые промышленностью БИС можно разделить на 2 класса: стандартные БИС и специализированные БИС. К стандартным БИС относятся широко тиражируемые микропроцессоры и наборы их поддержки, микросхемы памяти, сигнальные процессоры и т.п.

Специализированные БИС разделяются на несколько подклассов: полностью заказные ( Full Custom ), полузаказные ( Semi - Custom ) и программируемые пользователем ( Field Programmable ). Главным недостатком заказных и полузаказных специализированных БИС является высокая стоимость разработки устройств на их базе (порядка десятков-сотен тысяч долларов).

Комплексные ПЛИС ( CPLD ) представляют собой блоки логических вентилей объединенных программируемой коммутационной матрицей. Воздействуя на программируемые соединения коммутационной матрицы ПМЛ, можно реализовать требуемую схему. Современные CPLD , как правило, являются электрически перепрограммируемыми. CPLD сохраняют логическую структуру после отключения питания.

Микросхемы программируемых пользователями вентильных матриц FPGA ( Field Programmable Gate Arrays ) состоят из большого числа конфигурируемых логических блоков (зарубежный термин LUT ), и трассировочных ресурсов, обеспечивающих их межсоединения. Получение конкретной логической структуры на базе FPGA , реализуется путем прошивания в управляющие программируемыми межсоединениями триггеры (теневое ОЗУ) соответствующих значений. Ведущими разработчиками микросхем CPLD и FPGA являются фирмы Altera , Atmel , Lattice Semiconductor , Cypress Semiconductor , Xilinx.

В последнее время наблюдаются две тенденции: постоянное увеличение сложности разрабатываемых цифровых устройств и одновременное повышение гибкости и вычислительной мощности доступных аппаратных решений. Первая тенденция сделала востребованным появление принципиально новых средств проектирования и моделирования аппаратных цифровых устройств, а вторая сделала его возможным. В ходе своего развития системы автоматизированного проектирования (САПР) предназначенные для разработки цифровых устройств прошли несколько этапов.

Первые САПР для разработки аппаратных устройств имитировали их ручную разработку инженером – использовался механизм схемных редакторов и библиотеки микросхем.

На втором этапе (в 80-е – начале 90-х годов XX века) возникли языки описания аппаратуры ( HDL – Hardware Description Language ) и САПР с поддержкой этих языков. Предпосылкой к переходу на этот этап послужил массовый выпуск программируемых логических схем (ПЛИС) и появление реконфигурируемых микросхем класса FPGA.

Цель и задачи работы

- Анализ эффективности приложения существующих методов оптимизации управляющих автоматов с точки зрения аппаратных затрат, к управляющим автоматам, построенных на базе ПЛИС (CPLD и FPGA).

- Исследование существующих средств автоматизированной разработки цифровых устройств (в частности управляющих автоматов).

- Выработка новых методов автоматизированного проектирования управляющих автоматов и разработка программного обеспечения, поддерживающего эти методы.

Предполагаемая научная новизна

Научная новизна данной работы заключается в разработке новых методов автоматизированного проектирования управляющих автоматов. Эти методы строятся на уже разработанных и широко применяемых методов разработки и проектирование программного обеспечения, таких как архитектура, управляемая моделями (MDA - Model-Driven Design) и универсальный язык моделирования (UML - Unified Modelling Language). Также проведено исследование эффективности существующих методов оптимизации структуры управляющих автоматов, разработанных для заказных микросхем, для современных стандартных ПЛИС.

Планируемая практическая ценность

Разработываемое программное обеспечение можно будет использовать в качестве одного из элементов рабочего места разработчика цифровых устройств. Существующие продукты реализующие данную функцию отличаются большой ценой. В то же время в качестве базовой среды для разрабатываемого программного обеспечения была выбрана кроссплатформенная среда разработки приложений и систем Eclipse . Эта среда разработана и поддерживается всемирно известной компанией IBM . Среда распространяется на принципах OpenSource (бесплатно с открытым исходным кодом системы, с легальной возможностью последующего расширения функциональности пользователями системы) что выгодно отличает ее от остальных средств моделирования, используемых в настоящее время.

Обзор существующих разработок по теме

В настоящее время для описания логической структуры цифровых устройств, как правило, используются высокоуровневые языки описания оборудования ( Hardware Description Languages - HDL ). Наиболее распространенными среди них являются языки VHDL и Verilog . Однако непосредственная реализация управляющих автоматов на этих языках является трудоемким процессом. Поэтому в состав многих зарубежных САПР были включены специальные инструменты, позволяющие упростить разработку управляющих автоматов. Так в состав САПР Active - HDL фирмы Aldec включен модуль FSM . Этот модуль обладает многофункциональным графическим интерфейсом, для описания управляющих автоматов. Однако модуль FSM обладает рядом недостатков. В частности, форма записи управляющего автомата требует знания языка HDL . Так, условия и выдаваемые в операторных вершинах сигналы должны быть записаны в форме синтаксически правильных выражений выбранного языка описания оборудования. Главным недостатком модуля является отсутствие какой-либо оптимизации структуры получившего управляющего автомата. Код, генерируемый этой подсистемой, является неоптимальным с точки зрения затрат площади кристалла.

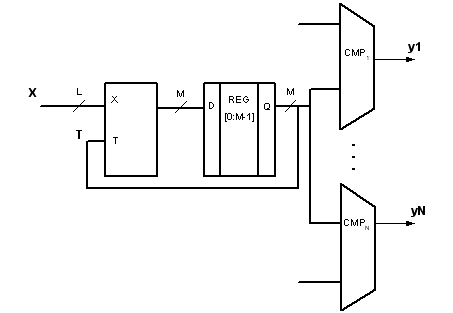

В ходе проведения исследования было установлено, что генерируемое модулем FSM поведенческое описание управляющего автомата реализуется средствами синтеза ( Synplify ) как автомат Мура с унарным кодированием состояний. Достоинством такой реализации является повышенное быстродействие, недостатком большие аппаратные затраты. Структурная схема этой реализации приведена на рисунке 1 [7].

Рисунок 1. Структура автомата с унарным кодированием состояний

Для такой структуры характерно большое количество используемых триггеров, по сравнению с традиционными реализациями. Число используемых триггеров равно: R = M , где M – число состояний графа. Однако при такой структуре упрощаются функции возбуждения автомата и, соответственно, логические схемы их реализующие. Это происходит благодаря унарному кодированию состояний, так как при этом кодировании в каждый терм функций возбуждения входит всего один разряд кода состояний T . То есть формула функции возбуждения (1) для такой структуры в общем случае содержит меньшее количество термов, чем при бинарном кодировании состояний автомата (2) (согласно статистике [ работа 1] средняя длина цепочки X находится в интервале от 1 до 1,2 ) [6]:

Также при унарном кодировании состояний автомата уменьшается количество необходимых для реализации схемы инверторов. Это происходит за счет отсутствия необходимости инвертирования разрядов кода состояний.

Таким образом, достоинствами этого метода, является меньшая сложность функций возбуждения (особенно проявляется при уменьшении разветленности автомата) и соответсвенно более высокое быстродействие автомата. Недостатками являются значительно большое количество используемых триггерных схем (особенно проявляется при увеличении состояний графа : R ~ M , при унарном кодировании; R ~ log 2 M , при бинарном кодировании ); и большая аппаратная затратность схем формирования выходных сигналов (при отсутствии в ПЛИС элементов XOR ).

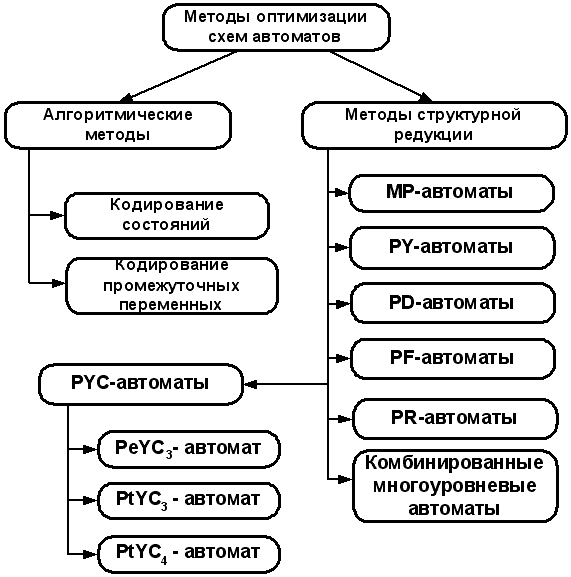

Известны, однако, и другие методы оптимизации структуры автоматов на ПЛИС. Классификация этих методов [1] приведена на рисунке 2.

Рисунок 2. Классификация методов оптимизации автоматов.

Однако в последнее время становится все более очевидным, что подобный подход к проектированию близок к исчерпанию своих возможностей. Появление новых, все более быстродействующих и содержащих большее количество логических ячеек на кристалле микросхем FPGA смещает приоритет при разработке устройств с минимизации аппаратных затрат в полученном устройстве или максимизации быстродействия полученного устройства – на обеспечение надежности и безупречной работы полученного устройства при максимально коротком цикле разработке.

Одним из наиболее перспективных способов разрешения этой проблемы является использование для проектирования аппаратных систем, средств основанных на ранее разработанных средствах проектирования сложных систем для программного обеспечения, таких как использование управляемой моделями архитектуры ( MDA – Model - Driven Architecture ) и унифицированный язык моделирование ( UML – Unified Modeling Language ).

MDA была предложена группой OMG ( Object Management Group ) в 2000 году [3]. Главной идеей MDA является описание сложных систем в виде набора моделей, стоящих на различных уровнях абстракции, относительно друг друга, и возможность преобразования моделей одного уровня в модели другого уровня абстракции [3]. Результатом таких преобразований является получение реализаций независимой от платформы модели, для различных платформ.

В настоящее время существует множество сред проектирования, поддерживающих управляемую моделями архитектуру и язык UML для описания моделей, которые ориентированы на разработку программного обеспечения ( Eclipse , Poseidon , ArgoUML и т.д.). Многие из этих сред являются расширяемыми продуктами (т.е. к ним можно подключать дополнительные модули сторонних разработчиков), поэтому было принято решение построить САПР для управляющих автоматов на базе одной из имеющихся сред проектирования.

В качестве базовой среды выбран Eclipse , это мотивировано тем, что это среда является легально бесплатным кроссплатформенным продуктом с открытым исходным кодом. Кроме этого Eclipse изначально разрабатывался как базовая расширяемая среда, поэтому в него включен развитый, хорошо документированный интерфейс подключения дополнительных модулей. Ряд подобных модулей уже разработан, в частности можно выделить модуль UniMod – предназначенный для автоматного ( SWITCH ) программирования. [4]

Текущие и планируемые результаты

На первом этапе работы над магистерской работой было проведено исследование применимости существующих методов[1,6] оптимизации структуры управляющих автоматов к современным стандартным ПЛИС[7].

В качестве исследуемых структур автомата были выбрана PYC – структура и структура с унарным кодированием. В качестве базовых ПЛИС для исследования выбраны ПЛИС компании Altera : EP1K10 (семейство ACEX1K) и EPM3032A (семейство MAX3000A). Микросхема EP1K10 относится к классу FPGA , микросхема EPM3032A относится к классу CPLD. Обе эти микросхемы отличает высокое быстродействие (частота тактирования до 250 МГц) и низкая стоимость (для EP1K10 – от 10$ до 20$, для EPM3032A от 1,7$ до 4$). Более подробные данные об этих ПЛИС приведены в приложении 3. Логическая мощность этих микросхем составляет: EP1K10 – 600 эквивалентных логических вентилей; EPM3032A – 600 логических ячеек ( LUT ).

Из анализа существующих проблем и требований вытекает необходимость программной реализации методов генерации структурного кода граф-автоматов и применение оптимизации этого кода.

Программный продукт должен обладать вышеперечисленными достоинствами (генерация структурного кода по заданному графу, подсчет требуемой площади кристалла и т.д.).

В ходе анализа методов оптимизации и постоянным расширением их числа появляются определенные требования к реализации программного продукта, формируется определенная структура.

Рисунок 3 - Структура разрабатываемой САПР (анимация 30 кадров, 6 к/с, 3 повторения, 6 КБайт)

Разрабатываемая система должна состоять из следующих частей:

• Графический редактор, который реализует возможность графического отображения, редактирования и создания требуемой граф-схемы (FSM).

• Компилятор, который дает возможность текстуального набора графа и приведение текстуального представления во внутренний язык программы (XML , XMI , или др.).

• Генератор кода с различными оптимизаторами, которые преобразуют внутренний код графа в конкретную (Мура или Мили) реализацию автомата. [7]

После реализации программного продукта будут проведены исследования относительно эффективности сгенерированного кода для различных существующих FPGA микросхем, будут построены графики зависимостей, а также результаты интеграции программы с различными существующими средствами синтеза.

Заключение и выводы

Результатом работы будет программное обеспечение, построенное на платформе Eclipse с открытым кодом и реализующая генерацию кода на языке HDL. Программный код будет сгенерирован с учетом существующих алгоритмов оптимизации управляющих автоматов и специфицирован под конкретную ПЛИС. Входными параметрами для ПО будет являться UML схема реализации управляющего автомата.

Список источников

1) А.А. Баркалов. Синтез устройств управления на программируемых логических устройствах. – Донецк. 2002.

2) В.М. Карпов. Теория автоматов. СПб. Питер. 2002.

3) OMG specifications, http://www. omg .org

4) Official website of UniMod , http://unimod.sourceforge.org

5) Часть 1. Технический обзор Платформы Eclipse – http://khpi-iip.mipk.kharkiv.edu/library/extent/prog/ETO/I.html

6) Зеленева И.Я. – «Методы синтеза многоуровневых структур управляющих автоматов на программируемых логических устройствах» – диссертационная работа.

7) Войтенко С.А. "Исследование методов проектирования управляющих автоматов на современных ПЛИС"

При написании данного автореферата магистерская работа еще не завершена. Окончательное завершение: январь 2007г. Полный текст работы и все материалы по теме могут быть получены у автора или руководителя после указанной даты.